|

| Thursday, 20 October 2016, 14:23 HKT/SGT | |

| |  | |

Source: Fujitsu Ltd | |

|

|

|

KAWASAKI, Japan, Oct 20, 2016 - (JCN Newswire) - Fujitsu Laboratories Ltd. today announced that it has collaborated with the University of Toronto to develop a new computing architecture to tackle a range of real-world issues by solving combinatorial optimization problems(1), which involve finding the best combination of elements out of an enormous set of element combinations. This architecture employs conventional semiconductor technology with flexible circuit configurations to allow it to handle a broader range of problems than current quantum computing(2) can manage. In addition, multiple computation circuits can be run in parallel to perform the optimization computations, enabling scalability in terms of problem size and processing speed. Fujitsu Laboratories implemented a prototype of the architecture using FPGAs(3) for the basic optimization circuit, which is the minimum constituent element of the architecture, and found the architecture capable of performing computations some 10,000 times faster than a conventional computer.

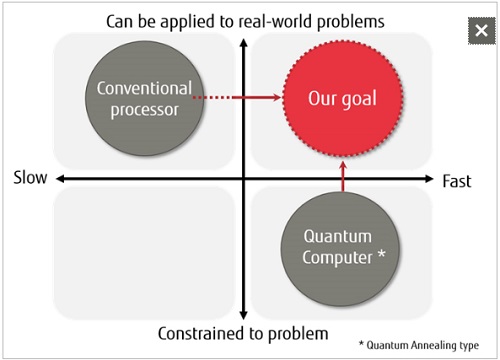

| | Fig. 1: Limits of conventional computing |

| | Fig. 2: Issues in methods to solve combinatorial optimization problems |

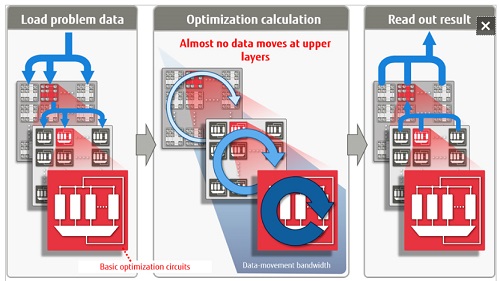

| | Fig. 3: The new architecture |

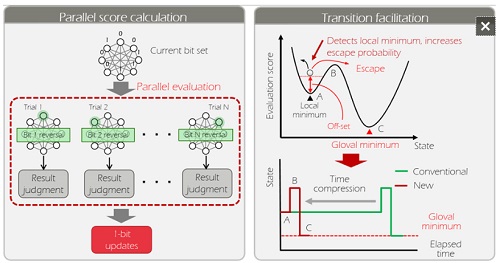

| | Fig. 4: Acceleration using basic optimization circuits |

Through this architecture, Fujitsu Laboratories is enabling faster solutions to computationally intensive combinatorial optimization problems, such as how to streamline distribution, improve post-disaster recovery plans, formulate economic policy, and optimize investment portfolios. It will also make possible the development of new ICT services that support swift and optimal decision-making in such areas as social policy and business, which involve complex intertwined elements.

Background

In society, people need to make difficult decisions under such constraints as limited time and manpower. Examples of such decisions include determining procedures for disaster recovery, optimizing an investment portfolio, and formulating economic policy. These kinds of decision-making problems--in which many elements are considered and evaluated, and the best combination of them needs to be chosen-are called combinatorial optimization problems. With combinatorial optimization problems, as the number of elements involved increases, the number of possible combinations increases exponentially, so in order to solve these problems quickly enough to be of any practical utility for society, there needs to be a dramatic increase in computing performance. The miniaturization that has supported the improvements in computing performance over the last 50 years is nearing its limits (Figure 1), and it is hoped that devices will emerge based on completely different physical principles, such as quantum computers.

Fig. 1: Limits of conventional computing

http://www.acnnewswire.com/topimg/Low_FujitsuQuantum11020.jpg

Fig. 2: Issues in methods to solve combinatorial optimization problems

http://www.acnnewswire.com/topimg/Low_FujitsuQuantum21020.jpg

Issues

Conventional processors have a great deal of flexibility in handling combinatorial optimization problems because they process these problems using software, but on the other hand, they cannot solve them quickly. Conversely, current quantum computers can solve combinatorial optimization problems quickly, but because they solve problems based on a physical phenomenon, there is a limitation of only adjacent elements being able to come into contact, so currently they cannot handle a wide range of problems. As a result, developing a new computing architecture that can quickly solve real-world combinatorial optimization problems has been an issue (Figure 2).

About the Technology

Using conventional semiconductors, Fujitsu Laboratories developed a new computing architecture able to quickly solve combinatorial optimization problems. This technology can handle a greater diversity of problems than quantum computing, and owing to its use of parallelization, the size of problems it can accommodate and its processing speed can be increased. Key features of the technology are as follows.

1. A new computing architecture for combinatorial optimization problems

The architecture uses a basic optimization circuit, based on digital circuitry, as a building block. Multiple building blocks are driven, in parallel, in a hierarchical structure (Figure 3). This structure minimizes the volume of data that is moved between basic optimization circuits, making it is possible to implement them in parallel at high densities using conventional semiconductor technology. In addition, thanks to a fully connected structure that allows signals to move freely within and between basic optimization circuits, the architecture is able to handle a wide range of problems.

2. Acceleration technology within the basic optimization circuit

The basic optimization circuit uses techniques from probability theory to repeatedly search for paths from a given state to a more optimal state. This includes a technique that calculates scores for the respective evaluation results of multiple candidates at once, and in parallel, when there are multiple candidates for the next state, which increases the probability of finding the next state (Figure 4, left). It also includes a technique that, when a search process becomes stuck as it arrives at what is called a "local minimum," it detects this state and facilitates the transition to the next state by repeatedly adding a constant to score values that increases the probability of escaping from that state (Figure 4, right). As a result, one can quickly expect an optimal answer.

Fig. 3: The new architecture

http://www.acnnewswire.com/topimg/Low_FujitsuQuantum31020.jpg

Fig. 4: Acceleration using basic optimization circuits

http://www.acnnewswire.com/topimg/Low_FujitsuQuantum41020.jpg

Results

Fujitsu Laboratories implemented the basic optimization circuits using an FPGA to handle combinations that can be expressed as 1,024 bits, and found that this architecture was able to solve problems some 10,000 times faster than conventional processors running a conventional software process called "simulated annealing." By expanding the bit scale of this technology, it can be used to quickly solve computationally intensive combinatorial optimization problems, such as optimizing distribution to several thousand locations, optimizing the profit from multiple projects with a limited budget, or optimizing investment portfolios. It can also be expected to bring about the development of new ICT services that support optimal decision-making at high speed.

Future Plans

Fujitsu Laboratories is continuing to work on improving the architecture, and, by fiscal 2018, aims to have prototype computational systems able to handle real-world problems of 100,000 bits to one million bits that it will validate on the path toward practical implementation.

(1) Combinatorial optimization problems

A class of problems that involves finding the minimum evaluation score for a combination of elements (such as policies, etc.).

(2) Quantum computer

A computing technology that takes advantage of quantum phenomena. A technique called "quantum annealing" has been developed to handle combinatorial optimization problems.

(3) FPGA

Field-programmable gate array. A general purpose device with a circuit layout that can be programmed after manufacture.

About Fujitsu Laboratories

Founded in 1968 as a wholly owned subsidiary of Fujitsu Limited, Fujitsu Laboratories Ltd. is one of the premier research centers in the world. With a global network of laboratories in Japan, China, the United States and Europe, the organization conducts a wide range of basic and applied research in the areas of Next-generation Services, Computer Servers, Networks, Electronic Devices and Advanced Materials. For more information, please see: http://www.fujitsu.com/jp/group/labs/en/.

Contact:

Fujitsu Laboratories Ltd.

Computer Systems Laboratory

E-mail: ngcs_qc_press_mem@ml.labs.fujitsu.com

Fujitsu Limited

Public and Investor Relations

Tel: +81-3-3215-5259

URL: www.fujitsu.com/global/news/contacts/

Topic: Press release summary

Source: Fujitsu Ltd

Sectors: Semiconductors, Electronics

http://www.acnnewswire.com

From the Asia Corporate News Network

Copyright © 2026 ACN Newswire. All rights reserved. A division of Asia Corporate News Network.

|

|

|

|

|

|

|

| Fujitsu Ltd |

| Mar 10, 2026 10:45 HKT/SGT |

|

Fujitsu launches Japan's first defense tech open innovation program |

| Mar 9, 2026 12:32 HKT/SGT |

|

Fujitsu and DT-Axis collaborate to advance digital health |

| Mar 3, 2026 20:00 HKT/SGT |

|

Fujitsu and BCN Port Innovation Foundation leverage ocean digital twin technology to drive the regeneration of the Port of Barcelona |

| Mar 2, 2026 10:55 HKT/SGT |

|

Fujitsu supports sustainable growth for retailers with data and AI through Uvance for Retail |

| Feb 27, 2026 11:03 HKT/SGT |

|

Fujitsu POS solution enhances customer experience at Hankyu Hanshin Department Stores |

| Feb 25, 2026 11:00 HKT/SGT |

|

Beisia Automates Supermarket Refrigerator Temperature Monitoring and Recording with Fujitsu's IoT Visualization Solution |

| Feb 24, 2026 10:23 HKT/SGT |

|

Fujitsu expands Uvance for Finance offerings to accelerate DX across financial sector |

| Feb 19, 2026 11:12 HKT/SGT |

|

Osaka Hospital launches project to safely utilize generative AI for healthcare workforce improvements |

| Feb 18, 2026 09:41 HKT/SGT |

|

Fujitsu named to FORTUNE Magazine's list of 'World's Most Admired Companie's for eighth year running |

| Feb 17, 2026 11:21 HKT/SGT |

|

Fujitsu automates entire software development lifecycle with new AI-Driven Software Development Platform |

| More news >> |

|

|

|

|